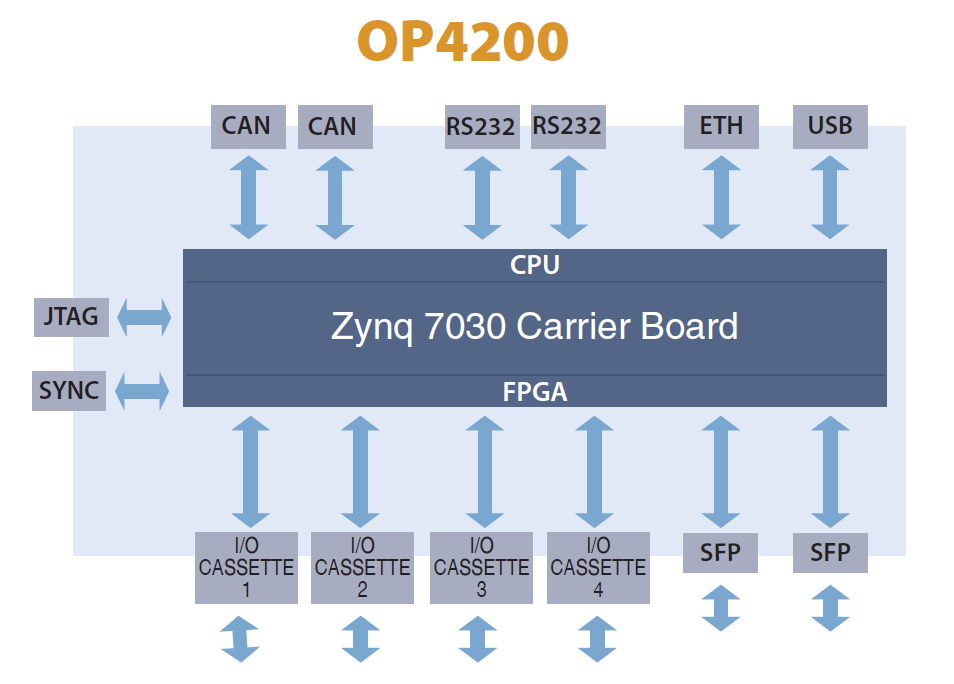

The OP4200 is part of the OPAL-RT line of simulation systems. It contains an SoC (system on chip) integrating an ARM CPU and a Kintex-7 FPGA, a high-end FPGA, signal conditioning for up to 128 I/O lines and two high-speed fiber-optic SFP ports. The design provides four slots for signal conditioning cassettes.

FEATURES

- 16GB SD

- 1024MB DDR3L

- Xilinx Zynq XC7Z030 all programmable SoC device with Dual-core ARM Processor Cortex A9 1GHz, Kintex-7 FPGA, 125K

- Linux-based real-time operating

- Four cassettes for analog or digital I/O interfaces

- Two high-speed communication ports

- Communication options: two CAN, two RS232, one Ethernet

I/O CONFIGURATIONS

The OP4200 simulator provides signal conditioning for up to 128 I/Os, which are managed from the PL (FPGA) section of the Zynq module.

The I/O lines are routed from the Zynq board to the four cassettes, through the OP4200’s carrier board.

The swappable cassettes provide signal conditioning flexibility. They are factory configured and their configuration information is processed by the system at boot time for initialization (I/O line direction, analog module calibration coefficients, etc.). During initialization, the boot system validates that the cassette type and position match the I/O configuration used in the model.